本文由 365源码网 – 18522379162 发布,转载请注明出处,如有问题请联系我们!RF前端,射频集成电路,完整的GPS解决方案。自动发货!#3

RF前端,射频集成电路,完整的GPS解决方案。自动发货!#3020

发货内容:

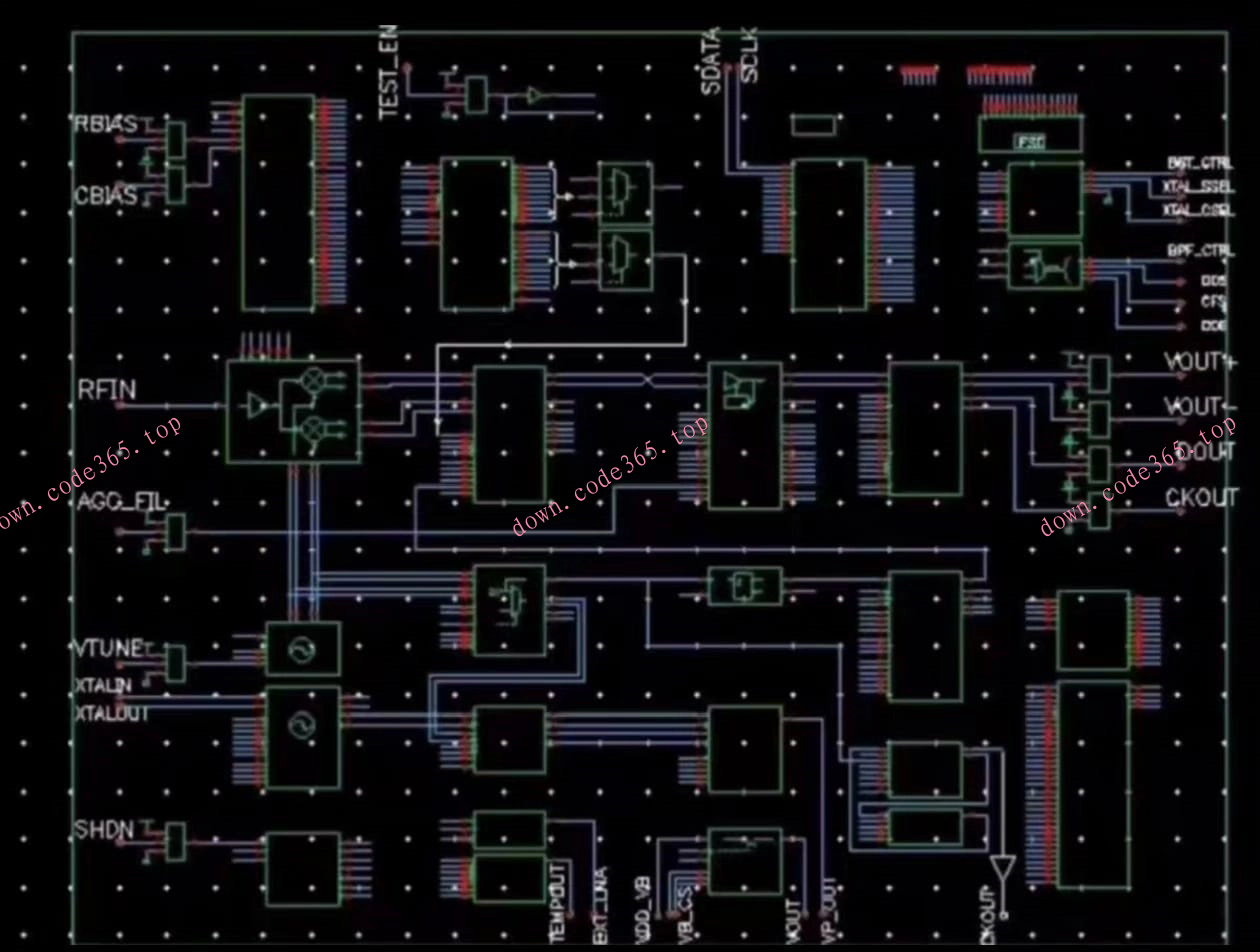

OA格式的工程文件,617618均可用

非别家的CDB格式(不能直接使用)。

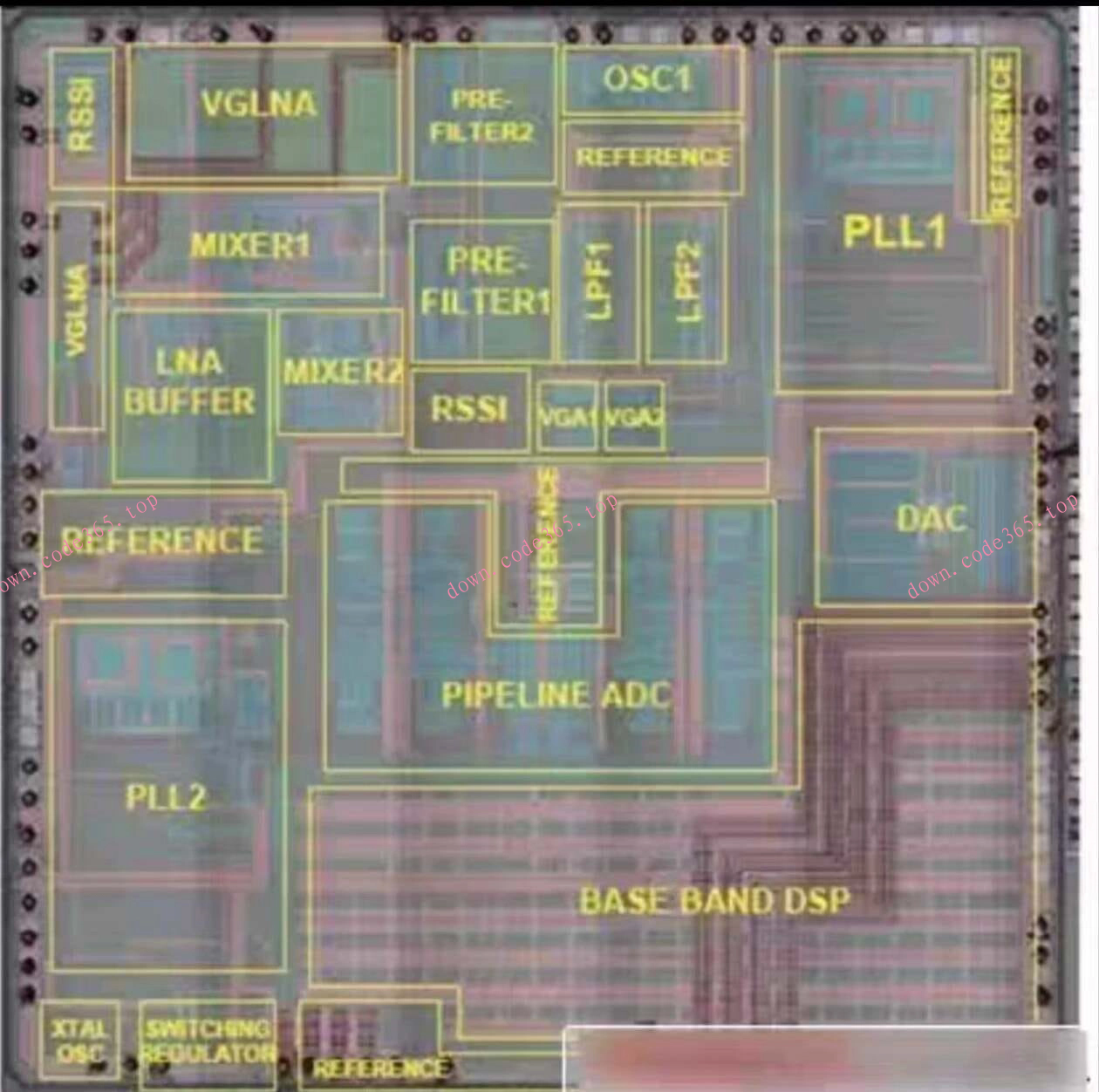

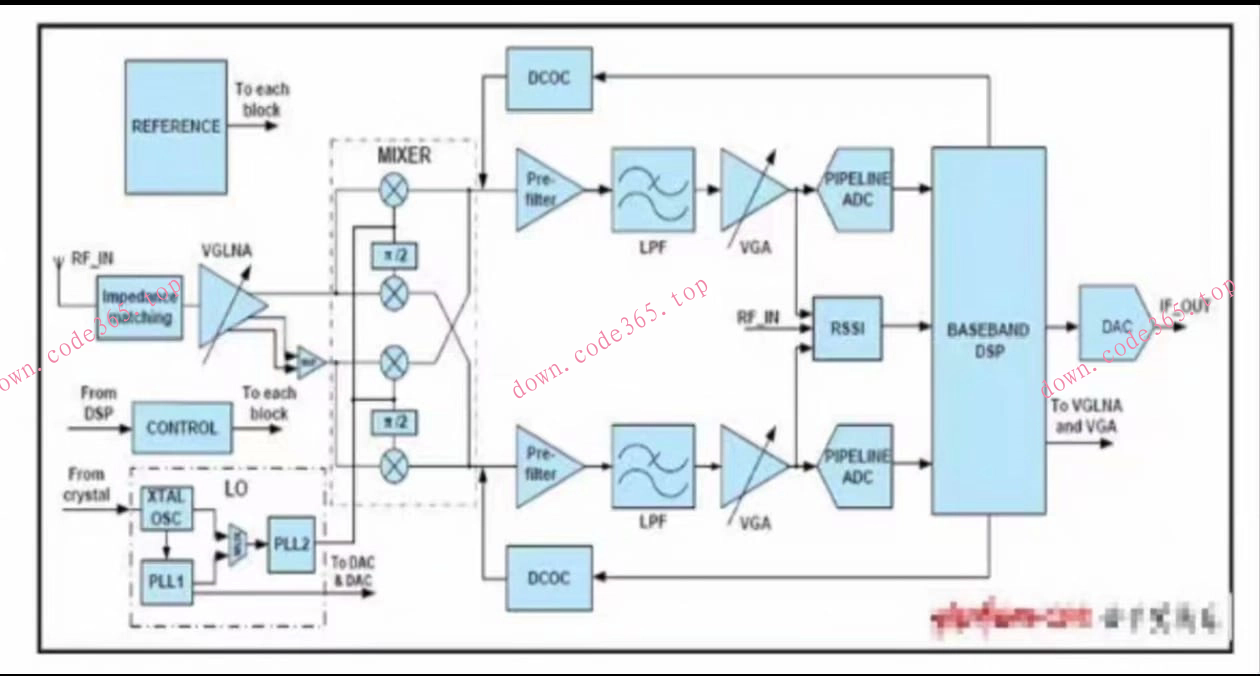

集成了低噪声放大器(LNA)、混频器、BPF、自动增益控制放大器(AGC)、本振频率合成器、时钟缓冲器和内部数字采样器。

cadence OA格式 仅供研究学习参考

不能直接仿真,可以替换为自己的PDK仿真一款高度集成的 GPS 接收器芯片,其内部包含以下关键电路模块:

1. 低噪声放大器(LNA)

- 功能:接收天线输入的微弱 GPS 信号(约 1575.42MHz),提供 24dB 增益,降低系统整体噪声系数(典型值 4.5dB),提升接收灵敏度。

2. 混频器(Mixer)

- 功能:将射频(RF)信号与本振(LO)信号混合,完成 下变频,生成中频(IF)信号(典型 IF 频率 1.023MHz)。

3. 带通滤波器(BPF)

- 结构:两级滤波器设计,包含 射频级滤波 和 中频级滤波。

- 作用:抑制带外干扰(如邻近频段噪声)和镜像频率干扰,典型镜像抑制达 18dB,中频滤波抑制带外毛刺超 60dB。

4. 自动增益控制(AGC)

- 功能:动态调整信号增益(动态范围 50dB),适应输入信号的强弱变化,防止过载并维持稳定的中频输出。

5. 本振频率合成器(LO Synthesizer)

- 组成:集成锁相环(PLL)和压控振荡器(VCO)。

- 作用:生成稳定的本振信号(频率由外部参考时钟控制),支持精确的下变频操作。

6. 时钟缓冲器(Clock Buffer)

- 功能:接收外部 18.414MHz 参考时钟(晶体或 TCXO),生成芯片内部所需时钟信号,同时为基带处理器提供同步时钟。

7. 数字采样器(Digital Sampler)

- 功能:将中频模拟信号转换为数字信号(通过 1-bit Σ-Δ ADC),输出至基带处理器进行后续解调与解码。

---

总结

通过集成上述模块,实现了从射频接收、信号调理到数字输出的完整 GPS 前端处理链路,仅需少量外围元件(如晶体、滤波电容等)即可构建完整的 GPS 接收系统。

(PS:E016

-拍下立马发货!

-由于具有可复制性,售出概不退换!

-学习自用,不得商用后果自负!

-内容自行消化!

#3020资料